使用Zybo Zynq开发板的WIDI无线HDMI

0

0

准备工作:

材料:

注:本教程假设读者熟悉Vivado设计套件,并具备创建新项目和模块设计经验。

项目需求如下:

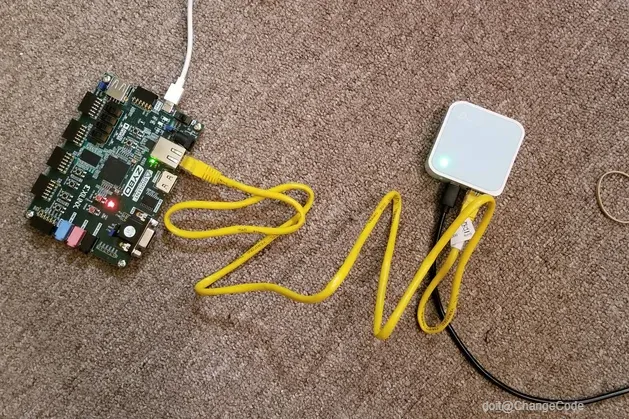

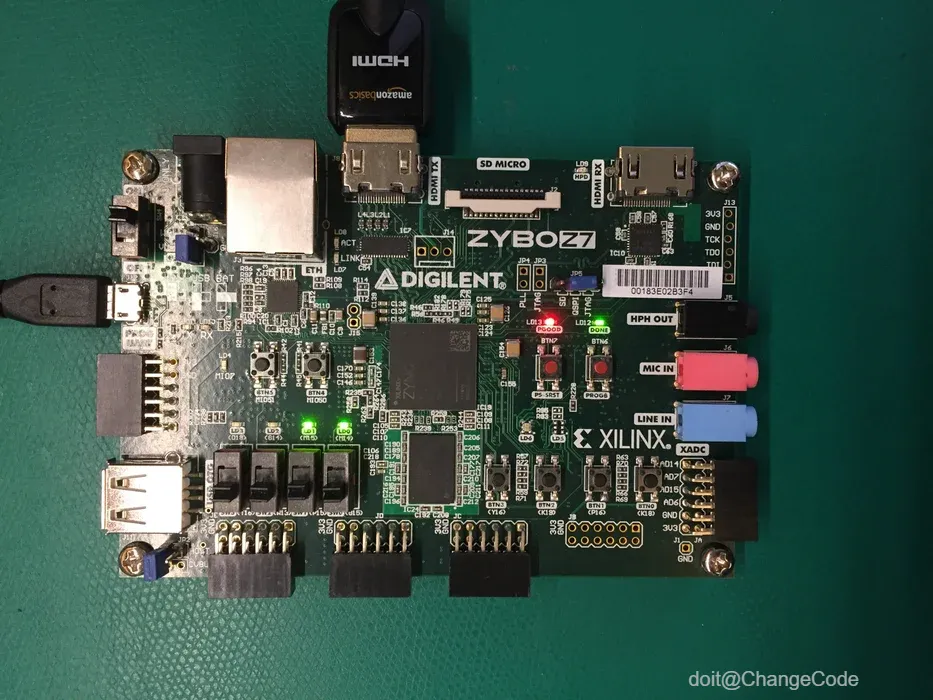

- 2块Digilent Zybo开发板(必须至少有一个HDMI端口)

- 2根HDMI线缆

- 2根Micro USB线缆(用于将Zybo连接到PC进行开发)

- 2台TP-Link WR802N微型路由器(包括额外的2根Micro USB线和墙壁电源适配器)

- 2根以太网线缆

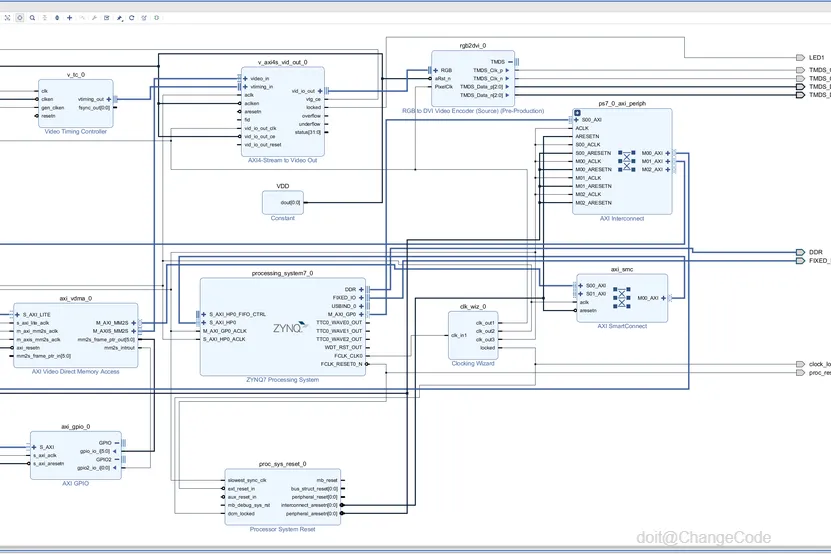

配置发射器的Zynq可编程逻辑

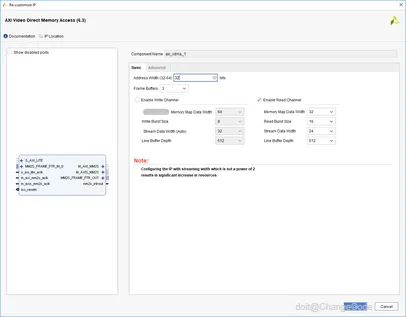

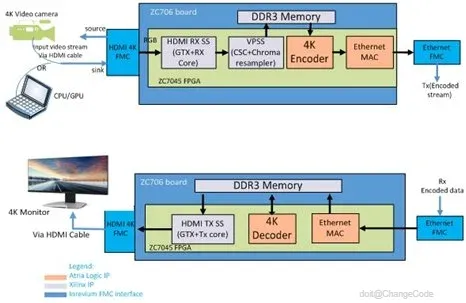

我们的开发方法是通过两个视频直接内存访问(VDMA)块实现从PC到显示器的HDMI直通。一个用于写入,一个用于读取。两者均选择自由运行模式,3帧缓冲区模式(0-1-2)。由于视频核心针对60帧/秒进行了优化,这意味着VDMA将以16.67毫秒的间隔依次写入或读取新帧:0,1,2,0,1,2,0,1,2。两个VDMA的DDR内存位置不同,因为它们不再同步。相反,使用硬件定时器(TTC1),配置为60Hz,用于同步两个内存位置之间的数据移动。

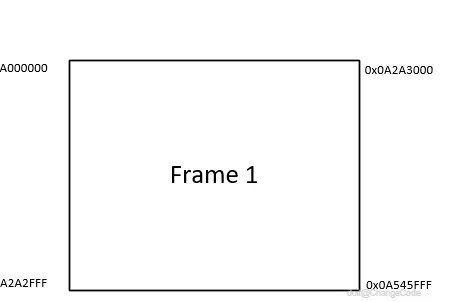

下图显示了3个帧及其尺寸和所需内存量。如果将写VDMA分配给这些内存位置,则可以将读VDMA的内存位置分配在此集之外,例如从0x0B000000开始。每个帧由1280×720像素组成,每个像素由8位红、绿、蓝组成,总共有24位。这意味着一个帧由1280×720×3字节(2.76MB)组成。

在定时器IRQ中处理两个VDMA内存位置之间的数据复制。VDMA提供当前正在写入或读取的帧的指针。该帧由特定的格雷码表示,需在软件中进行转换。3帧缓冲区配置的格雷码定义可以在《AXI VDMA产品指南》附录C中找到。

此方法允许在不读取当前正在写入的帧的情况下复制其内容。注意:接收数据时不使用读VDMA。其唯一目的是验证从写VDMA复制内存的正确操作。应禁用读VDMA。

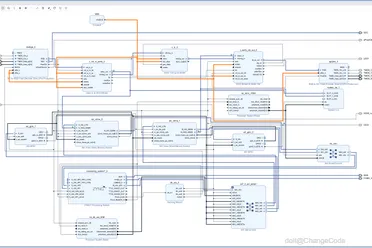

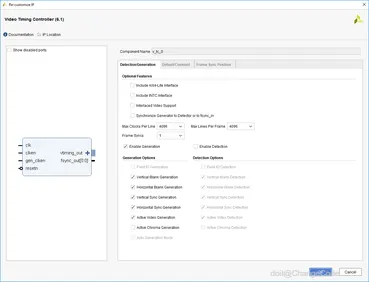

以下是创建发射器设计模块的步骤:

- 创建新项目时,建议为项目分配芯片或板卡。

- 添加以下模块:

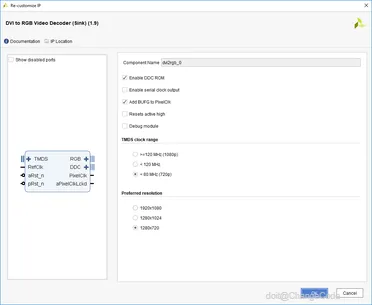

- dvi2rgb

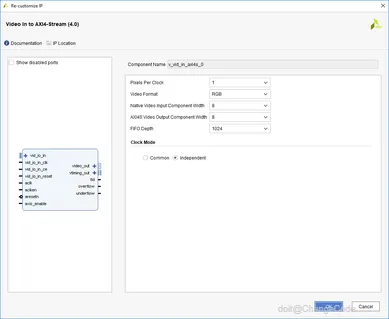

- 视频输入到AXI4-stream

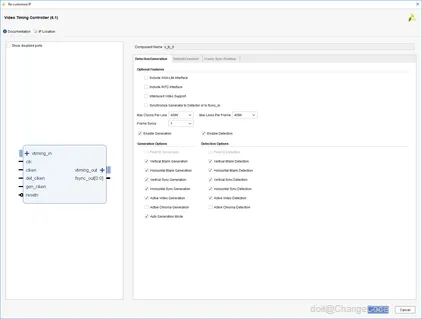

- 定时控制器

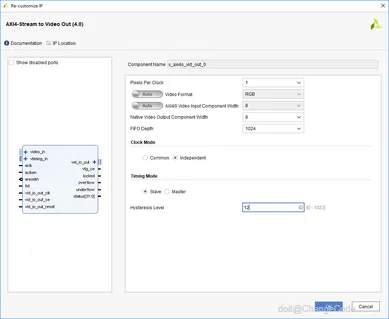

- AXI4-stream到视频输出

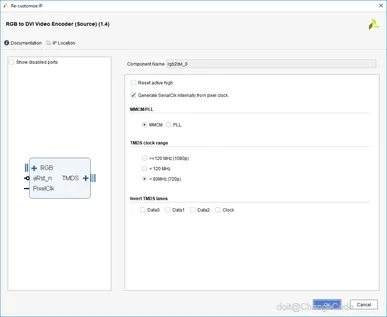

- rgb2dvi

- AXI VDMA ×2

- AXI GPIO ×2

- 时钟向导

- 常量

- Zynq处理系统

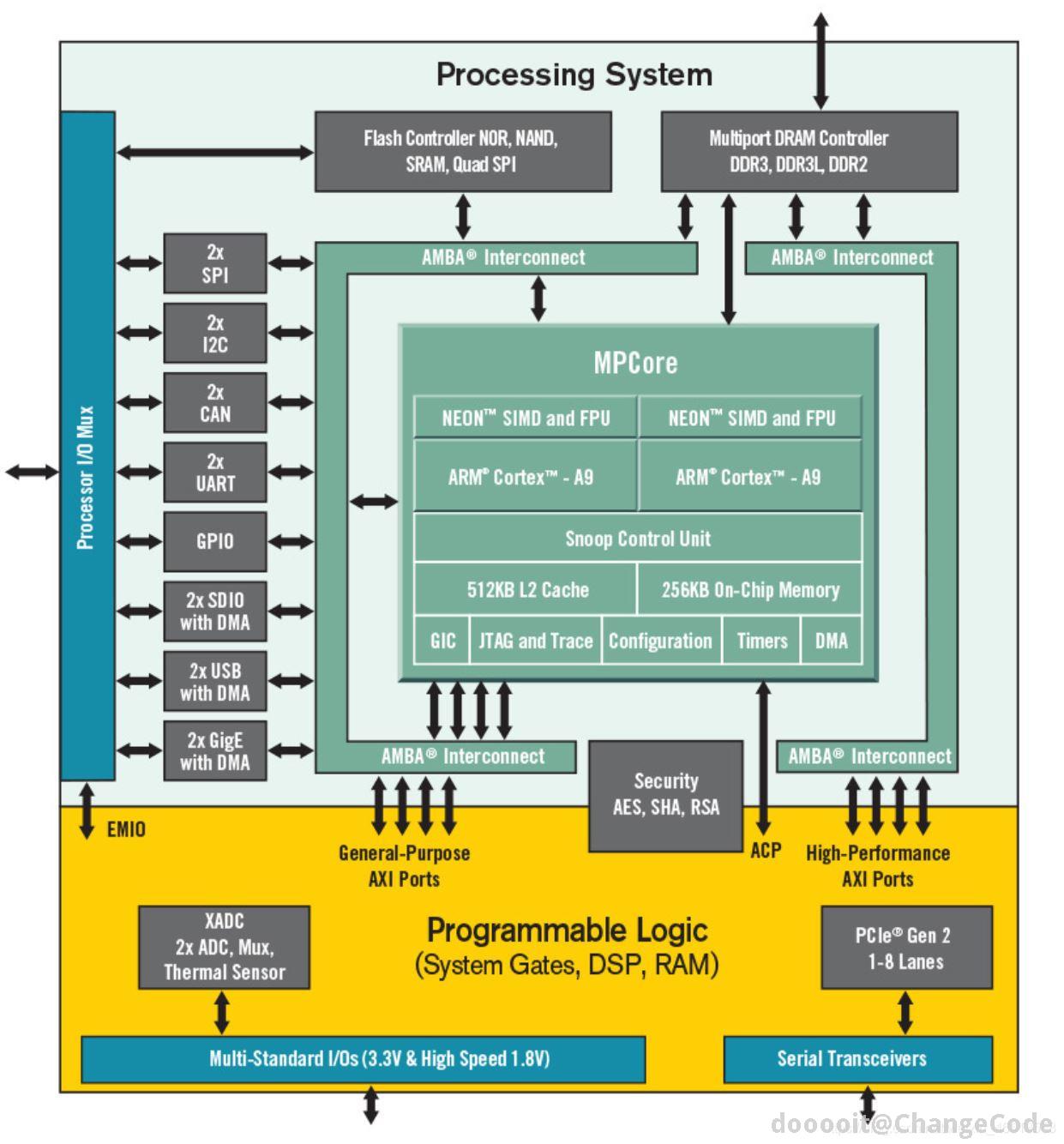

- 配置Zynq处理系统:

- 在PS-PL配置中启用M AXI GPO接口。

- 启用HP0和HP1接口。

- 启用I/O外设中的ENET0和应用程序处理器单元中的Timer0。

- 设置PL Fabric Clocks为100 MHz。

- 运行连接自动化工具,确保连接与发射器模块设计图匹配。

- 创建HDL包装器。

配置接收器的Zynq可编程逻辑

接收器的可编程逻辑模块更简单。主要区别在于缺少HDMI输入模块和恢复的像素时钟。因此,必须从时钟向导生成自己的像素时钟。此设计应在与发射器不同的项目中完成。接收器项目遵循Zybo 7Z-20板,而发射器遵循Z7-10板。

以下是创建接收器设计模块的步骤:

- 添加以下IP模块:

- 定时控制器

- AXI4-stream到视频输出

- RGB到DVI

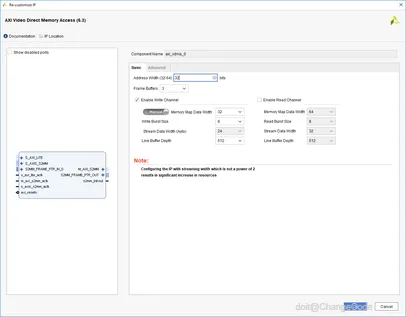

- AXI VDMA

- AXI GPIO

- 处理系统

- 时钟向导

- 配置VDMA仅用于读取通道,禁用写入通道。

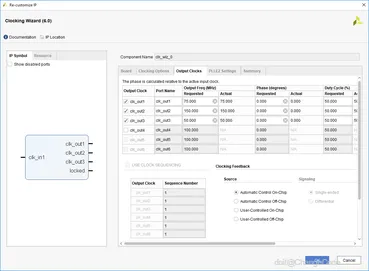

- 配置时钟向导输出:

- clk_out1: 75 MHz(像素时钟)

- clk_out2: 150 MHz(流时钟)

- clk_out3: 50 MHz(AXI-Lite时钟)

- 运行连接自动化工具,确保连接与接收器模块设计图匹配。

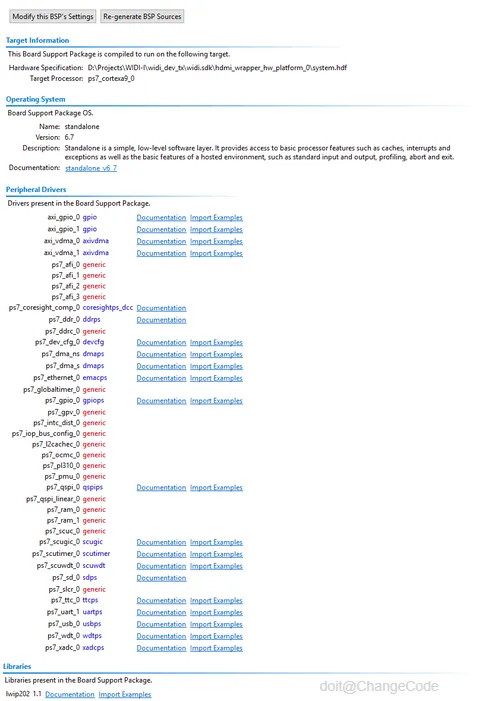

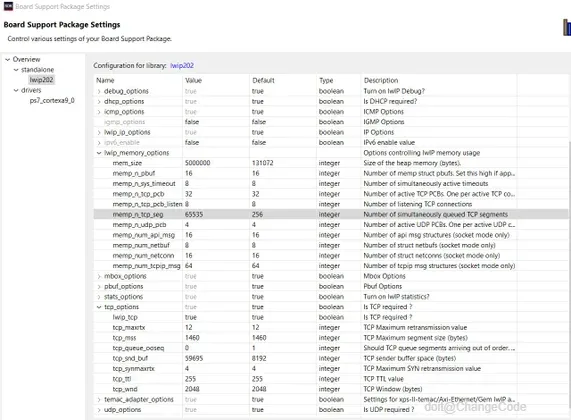

设置VDMA驱动程序

使用BSP中的示例项目作为参考,配置通过AXI-Lite接口的不同模块。打开系统.mss文件,查看块设计中的外设驱动程序。使用“导入示例”选项导入利用这些外设的示例项目,学习如何在软件中使用Xilinx驱动程序配置它们。

TX中断处理函数(IRQHandler)

此函数通过GPIO块读取读写VDMA提供的格雷码。将格雷码转换为十进制,用于选择当前帧的基础内存位置。仅捕获每第6帧以将帧速率降低到10 Hz。取消注释代码中的两行可切换到HDMI直通模式进行调试。

RX中断处理函数(IRQHandler)

此函数类似于TX函数,但从以太网使用的双缓冲FIFO复制数据。以太网代码指示正在写入FIFO的帧,数据从与VDMA读取帧相对的帧复制,以避免撕裂。

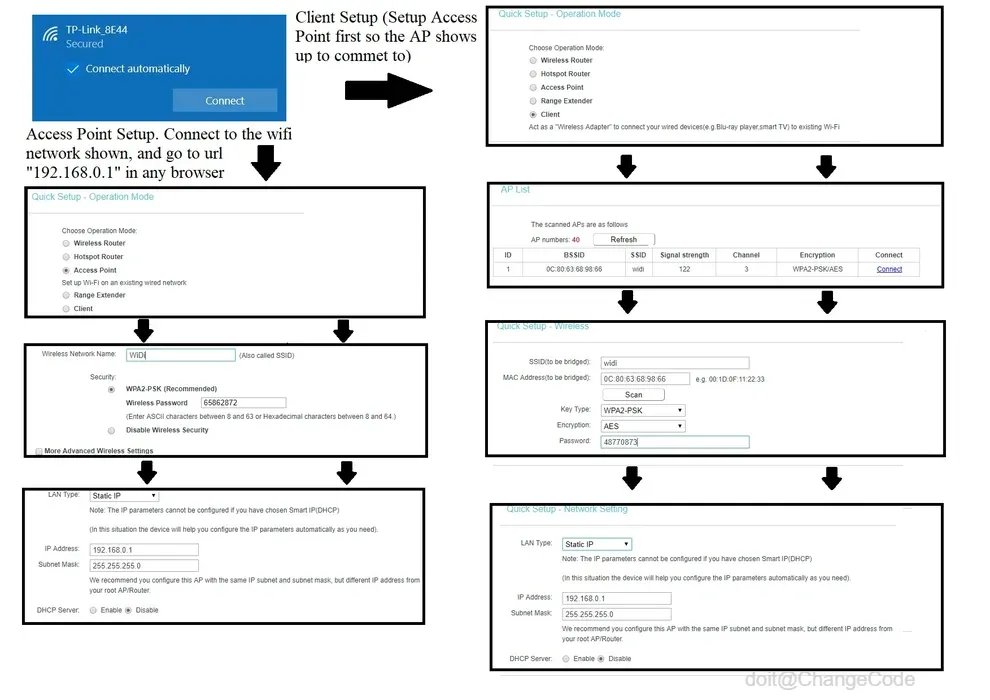

设置纳米路由器网络

- 分别启动两个TP-Link纳米路由器,连接到默认的Wi-Fi SSID。

- 将其中一个设备设置为接入点,命名为已知网络并禁用DHCP。

- 将另一个设备设置为客户端,连接到接入点的SSID并禁用DHCP。

- 确保客户端成功连接到接入点,LED指示灯常亮。

设置Zynq处理系统通过以太网传输数据

利用Vivado SDK中的示例项目,学习如何使用LwIP TCP操作。传输过程如下:

- 使用裸机LWIP驱动程序函数调用初始化TCP网络。

- 指定必要的网络操作回调函数。

- 通过IP地址和端口连接到接收器。

- 当VDMA驱动程序定时器到期时,进入TX ISR。

- 根据VDMA格雷码确定当前帧缓冲区。

- 将数据段排队到TCP发送缓冲区并输出数据。

- 在收到确认后,排队下一个数据段。

- 重复步骤6和7直到帧传输完成

设置Zynq处理系统通过以太网接收数据

接收设备操作与发射设备类似:

- 初始化TCP网络并指定IP地址。

- 接收以太网数据包并复制到网络缓冲区。

- 使用双数据缓冲区避免覆盖数据。

- 当VDMA定时器到期时,进入RX ISR。

- 根据VDMA格雷码确定当前帧缓冲区。

- 将网络缓冲区的数据复制到VDMA的三重帧缓冲区。

连接HDMI源和接收设备

连接发射器和接收器的HDMI线缆,编程FPGA并运行处理系统。由于LwIP操作的开销和带宽限制,帧率可能非常低。如有问题,通过UART连接识别警告或错误。

改进建议

- 实时视频压缩:在硬件或软件中实现实时视频压缩可显著减少所需数据量。

- 硬件以太网流:使用AXI以太网IP和FIFO缓冲区或DMA可提高数据传输效率。

可访问性与安全性

- 可访问性:最终产品应是一个完全集成的紧凑设备,用户可轻松连接到任何HDMI源并通过无线方式传输到显示器。

- 安全性:集成传输层安全(TLS)和有限的自动连接功能,确保隐私保护。

0

0 0

0 0

0 qq空间

qq空间  微博

微博  复制链接

复制链接  分享

分享